# Проблемы и направления развития микросхем с перевёрнутым кристаллом

А.М. Баранов<sup>1</sup>, А.А. Подковыров<sup>2</sup>, А.В. Андреев<sup>3</sup>

<sup>1</sup>ФГУ ФНЦ НИИСИ РАН, Москва, Россия, baranov@niisi.ras.ru;

<sup>2</sup>ФГУ ФНЦ НИИСИ РАН, Москва, Россия, barfey@cs.niisi.ras.ru;

<sup>3</sup>ФГУ ФНЦ НИИСИ РАН, Москва, Россия, alandreev@cs.niisi.ras.ru

**Аннотация.** В работе описываются проблемы и направления развития микросхем с перевёрнутым кристаллом. Рассматриваются особенности и свойства полимерных и LTCC подложек. Приводятся основные характеристики микросхем, разработанных в ФГУ ФНЦ НИИСИ РАН. Описана технология «система в корпусе» и ее преимущества.

**Ключевые слова:** технология перевернутого кристалла, низкотемпературные керамические подложки, полимерные подложки, система в корпусе

## 1. Введение

Мировой рынок полупроводниковых устройств постоянно стремится к созданию более компактных, быстрых, энергоэффективных микросхем для различных применений, начиная от мобильных устройств до серверов. Технология микросхем с перевёрнутым кристаллом является основным направлением создания высокопроизводительных микросхем. Однако при переходе к этой технологии возникают вызовы, связанные с производством, надежностью, применяемыми материалами, способностью противостоять внешним воздействиям. Исследование и разработка различных подложек, новых материалов, методов сборки и технологий тестирования играют важную роль в преодолении этих проблем и в успешном внедрении микросхем с перевёрнутым кристаллом на рынок.

## 2. Особенности полимерных и низкотемпературных керамических подложек

Подложка является одной из ключевых составляющих микросхемы, предоставляющей механическую поддержку и электрическую изоляцию для компонентов. Перевёрнутые кристаллы обычно изготавливаются по технологическим нормам от 90 нм и ниже и могут содержать матрицу из более 10 тысяч контактов (бампов) [1]. Соответствующие подложки должны обеспечить такой кристалл надлежащим количеством входных и выходных сигналов, а также питанием и землей. Это достигается с помощью матрицы, как правило, шариковых выводов (BGA) необходимого размера. В ряде случаев шариковые выводы могут не устанавливаться, тогда такая микросхема определяется как без выводов (например, как LGA – Land Grid Array).

В зависимости от конкретных требований и характеристик микросхемы, используются полимерные или низкотемпературные керамические подложки. Каждая из них имеет свои технологические особенности.

### 2.1. Полимерные подложки

Материал полимерных подложек, такой как Bismaleimide Triazine (BT resin) и его аналоги обладает рядом уникальных свойств (термостойкость и высокие температуры стеклования ( $>250^{\circ}\text{C}$ ), низкие диэлектрические константы, хорошая адгезия к проводящим материалам и композитам, огнестойкость) [2].

#### 2.1.1. Воздействие повышенных температур

Высокие температуры стеклования полимеров в составе подложки позволяют безболезненно производить кратковременный нагрев микросхемы при её монтаже на печатную плату модуля. Однако длительное воздействие повышенной температуры может приводить к искажению формы подложки. Так, например, после электротермотренировки при  $140^{\circ}\text{C}$  нами наблюдалось отклонение микросхемы от плоской формы в сторону сферичности, не позволяющее припаять микросхему на печатную плату модуля. Поэтому с своей документации мы не рекомендуем эксплуатировать микросхемы на полимерных подложках при температурах, превышающих  $85^{\circ}\text{C}$ . Дополнительно для минимизации искажения плоскости подложки необходимо следить за одинаковостью заполнения металлом симметричных слоёв подложки.

#### 2.1.2. Влагоустойчивость

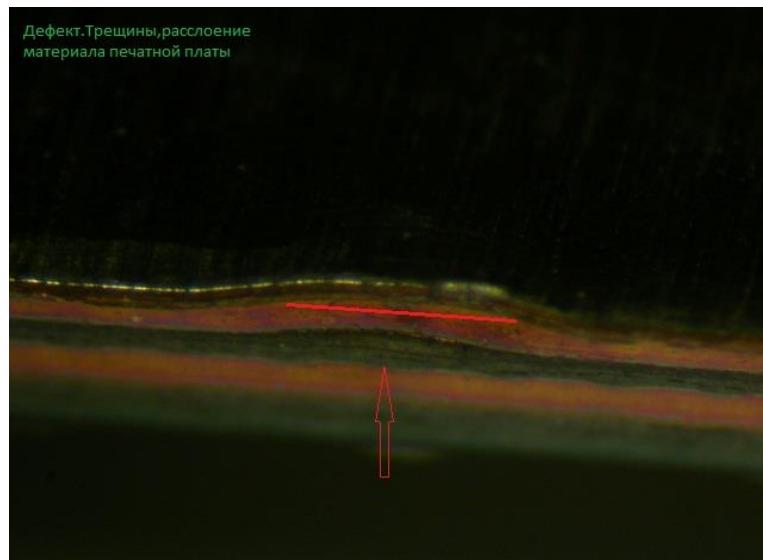

Полимерный подложки способны поглощать влагу. Поэтому они должны храниться либо в вакуумной упаковке, либо в шкафах сухого хранения. В основном полимерный подложки относятся к уровню<sup>3</sup> чувствительности к влажности по стандарту IPC/JEDEC J-STD-020C. Такие микросхемы в соответствии с данным стандартом после вскрытия упаковки должны быть установлены с модули в течении 168 часов. Кроме того, перед монтажом они должны быть выдержаны 24 часа в печи при температуре  $125^{\circ}\text{C}$  для удаления влаги. В противном случае, при монтаже микросхемы вода перейдёт в пар и может

произойти расслоение подложки (рисунок 1).

Рис. 1. Расслоения материала печатной платы подложки

### 2.1.3. Число слоёв

Полимерные подложки имеют технологическое ограничение на количество слоёв. Технология для подложек с числом слоёв, превышающим 14 (7-2-7 и более) считается производителем как «рискованная». При этом уменьшается выход годных подложек, и, соответственно, сильно возрастает их стоимость.

## 2.2. Подложки из низкотемпературной керамики

Технология низкотемпературной керамики (LTCC, Low Temperature Co-fired Ceramics) в настоящее время быстро развивается и успешно используется для производства ВЧ- и СВЧ-схем низкой и средней степени интеграции, телерадиовещания, телекоммуникаций, мобильной связи, портативных компьютеров и других приборов. Основными потребителями изделий на основе LTCC являются производители электронной аппаратуры, выпускающие как изделия массового потребления, так и двойного назначения.

При этом LTCC подложки не уступают полимерным подложкам в эффективности передачи высокоскоростных сигналов.

### 2.2.1. Стоимость

Стоимость LTCC подложки для перевёрнутых кристаллов зависит от материала проводника. Стоимость подложки с серебряными проводниками может превышать стоимость подложки с медными проводниками в 10 – 100 раз (в зависимости от размера). Это делает использование серебросодержащих паст в подложках коммерчески не приемлемым для массового производства.

Медносодержащие LTCC подложки

несколько дороже полимерных подложек. Однако такие подложки являются безальтернативным решением для высокоскоростных микросхем с перевёрнутым кристаллом в условиях, когда окружающая среда не позволяет использовать полимерные подложки (расширенный диапазон температур, повышенная влажность, длительное воздействие радиации, вакуум).

### 2.2.2. Механическая прочность

Для микросхем с высокоскоростными интерфейсами обмена информацией одним из основных требований является соблюдение необходимого волнового сопротивления для дифференциальных пар. Геометрические параметры проводников определяются моделированием исходя из данных производителя подложек (параметры проводника и изолятора, толщины слоёв керамики и т.п.). Например, в разработанной ФГУ ФНЦ НИИСИ РАН микросхеме маршрутизатора RapidIO для вывода высокоскоростных сигналов RapidIO от перевёрнутого кристалла до шариковых выводов на подложке с обеспечением необходимого волнового сопротивления дифференциальных пар было использовано 17 слоёв LTCC керамики толщиной 75 мкм и 50 мкм с медными проводниками. При этом толщина подложки составила  $1,15 \pm 0,12$  мм при размере 31 x 31 мм. Остеклованная керамика такой толщины оказалась довольно хрупкой (см. рисунок 2) и потребовала повышенной осторожности при проведении испытаний.

Рис. 2. Разрушение подложки из LTCC керамики

### 2.3. Сложность подложек

Изначально подложки для перевёрнутых кристаллов более сложные по сравнению с подложками для микросхем с проволочным соединением кристалл-корпус. Это связано с тем, что требуется развести сигналы, земли и питания с огромного количества бампов на кристалле через подложку к шариковым выводам. Задача решается путём использования большого количества слоёв проводников со слепыми переходными отверстиями. Во множестве слоёв удаётся с нужными

требованиями развести скоростные сигналы, обеспечить надлежащее питание. При этом количество слоёв ограничивается возможностями производства и ценой подложки.

На рисунке 3 приведены данные по числу слоёв в подложках, разработанных в ФГУ ФНЦ НИИСИ РАН.

В таблице 1 приведены основные размеры разработанных в ФГУ ФНЦ НИИСИ РАН подложек.

Рис. 3. График количества слоев подложек, разработанных в ФГУ ФНЦ НИИСИ РАН, по годам

Из графика видно, что для полимерных подложек (перечень из таблицы 1), как правило, достаточно 12-14 слоёв подложки чтобы надлежащим образом развести сигналы, земли и питания от кристалла к шариковым выводам. В то время, как для LTCC подложек для решения аналогичной задачи требуется большее количество слоёв: около 20 и выше. Это объясняется тем, что в керамике размеры проводников и зазоров между ними значительно больше, чем в полимерной подложке (~75 мкм против ~15 мкм), и требуется больше слоёв, чтобы развести сигналы.

На графике выделяется высокое количество слоёв (36) для LTCC подложки для микросхемы на рисунке 2. Это объясняется наличием в микросхеме большого количества интерфейсов ввода вывода, в том числе 8 каналов последовательного RapidIO (2,5 Гбит/с), для разводки сигналов и питаний которых и потребовалось такое количество слоёв.

Размеры подложек для перевёрнутых кристаллов определяются исходя из двух соображений:

- количество шариковых выводов в матрице должно быть необходимым и достаточным для вывода/вывода всех сигналов и обеспечения микросхемы необходимым питанием;

- по возможности унифицировать матрицы шариковых выводов в минимальное количество типоразмеров.

Из таблицы видно, что до сих пор в основном использовались три размера подложек: 21x21 мм, 31x31 мм, 37,5x37,5 мм. Это позволило сэкономить на оснастке для испытания микросхем, в частности использовать унифицированные контактирующие устройства (КУ). На сегодняшний день, в связи с развитием направления по созданию коммерческих микросхем, основным приоритетом становится максимальное уменьшение цены микросхемы при серийном производстве. Возникла необходимость минимизации параметров подложки. Типичном примером такого подхода является промышленный контроллер, разработанный ФГУ ФНЦ НИИСИ РАН. Характеристики подложки для этого контроллера приведены в строке 14 таблицы 1.

Таблица 1. Основные характеристики разработанных flip-chip корпусов

| Микросхема (порядковый номер) | Материал подложки | Размер подложки (мм) | Матрица шариковых выводов (шаг 1 мм) | Кол-во слоев подложки | Дата разработки (мес. год) |

|-------------------------------|-------------------|----------------------|--------------------------------------|-----------------------|----------------------------|

| 1                             | LTCC              | 31 × 31              | 30 x 30                              | 23                    | авг.12                     |

| 2                             | полимер           | 37,5 × 37,5          | 36 x 36                              | 5-2-5 (12)            | апр.14                     |

| 3                             | полимер           | 37,5 × 37,5          | 36 x 36                              | 5-2-5 (12)            | авг.15                     |

| 4                             | полимер           | 31 × 31              | 30 x 30                              | 6-2-6 (14)            | апр.17                     |

| 5                             | полимер           | 31 × 31              | 30 x 30                              | 7-2-7 (16)            | сен.17                     |

| 6                             | полимер           | 21 × 21              | 20 x 20                              | 5-2-5 (12)            | ноя.17                     |

| 7                             | LTCC              | 31 × 31              | 30 x 30                              | 36                    | сен.18                     |

| 8                             | LTCC              | 31 × 31              | 30 x 30                              | 21                    | апр.19                     |

| 9                             | полимер           | 37,5 × 37,5          | 36 x 36                              | 6-2-6 (14)            | май.19                     |

| 10                            | LTCC              | 31 × 31              | 30 x 30                              | 18                    | июн.19                     |

| 11                            | LTCC              | 31 × 31              | 30 x 30                              | 17                    | июл.19                     |

| 12                            | полимер           | 31 × 31              | 30 x 30                              | 6-2-6 (14)            | авг.19                     |

| 13                            | полимер           | 37,5 × 37,5          | 36 x 36                              | 6-2-6 (14)            | июл.20                     |

| 14                            | полимер           | 17 × 17              | 16 x 16                              | 1-1-1-1 (4)           | сен.20                     |

### 3. Рост сложности кристаллов процессоров и контроллеров

Производство чипов для микросхем является высоконецентрированным бизнесом. Ведущие

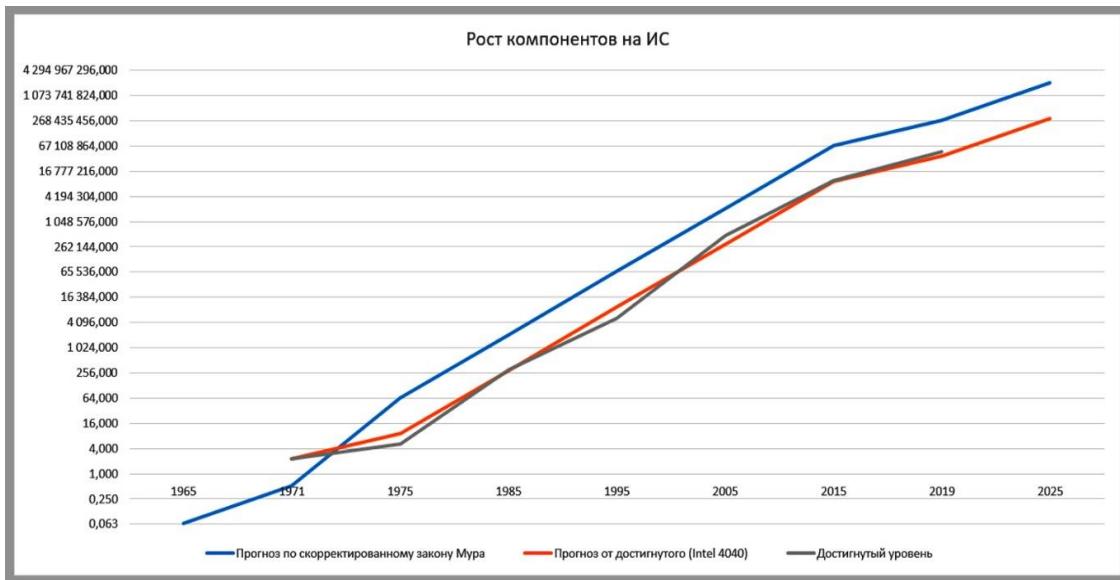

производители вкладывают огромные деньги в развитие технологий, позволяющей еще уменьшить размеры транзисторов и проводников на кристалле. Развитие технологии описывается законом Мура: количество транзисторов на кристалле удваивается

примерно каждые два года. Закон был сформулирован основателем Intel Гордоном Муром в 1965 году, и это закон продолжает работать вплоть до сегодняшнего дня (рис. 4) [3]. Здесь приведен анализ закона Мура, где сравнивается прогноз с достигнутым уровнем. Для построения графика с использованием математического ряда авторы выбрали две отправные точки: данные Мура (64 компонента в 1965 году) и число компонентов на первой ИС

Intel 4040:

Прогноз по скорректированному Муром закону с начальной величиной в 64 компонента оказался явно более оптимистичным (синяя линия). А прогнозный ряд с отправной от Intel 4040 величины (красная линия) практически совпадает с реально достигнутыми результатами (чёрная линия). По оси X указаны годы, а по оси Y указано число транзисторов на кристалле.

Рис. 4. График роста компонентов на ИС

Уменьшение размера транзисторов даёт возможность повысить их плотность на кристалле, увеличить их количество, соответственно, поднять вычислительные возможности микросхемы. Появляется возможность ввести в состав кристалла множество вычислительных ядер, позволяющих распараллелить решение различных задач и управлять обменом с внешними устройствами независимыми потоками данных.

Для решения задач многопоточности в состав кристалла интегрируется набор контроллеров высокоскоростных интерфейсов для связи и обмена информацией с соседними устройствами в виде сложно-функциональных блоков (СФ-блоки), таких как RapidIO, SATA, PCIe, USB, Gigabit Ethernet, DDR и другие. Конкретный набор СФ-блоков для каждой разрабатываемой микросхемы определяется исходя из технического задания. Схема построение микросхемы, когда в одном кристалле размещаются все необходимые контроллеры и процессорные ядра, принято называть системой на кристалле (СнК).

#### 4. Переход на систему в корпусе

Обратной стороной миниатюризации элементов кристаллов является возрастание стоимости производства пластин по

уменьшенным технологическим нормам. Например, стоимость первоначального запуска новых пластин с кристаллами по технологии 28 нм у одного из ведущих производителей (фабрика TSMC, Тайвань) превышает \$1 млн. Запуск пластин по технологии 12 нм и ниже будет обходиться значительно дороже.

Соответственно возрастает цена ошибки в разрабатываемой топологии кристалла. Наличие ошибки в одном из СФ-блоков может привести к неработоспособности всей микросхемы и напрасно потраченным ресурсам, опозданием с выходом на рынок. Таким образом, по мере усложнения технологии изготовления кристаллов СнК сталкивается с нарастающими сложностями. Решением этой проблемы стала дезинтеграция кристалла, т.е. переход от «системы на кристалле» к «системе в корпусе» (СвК).

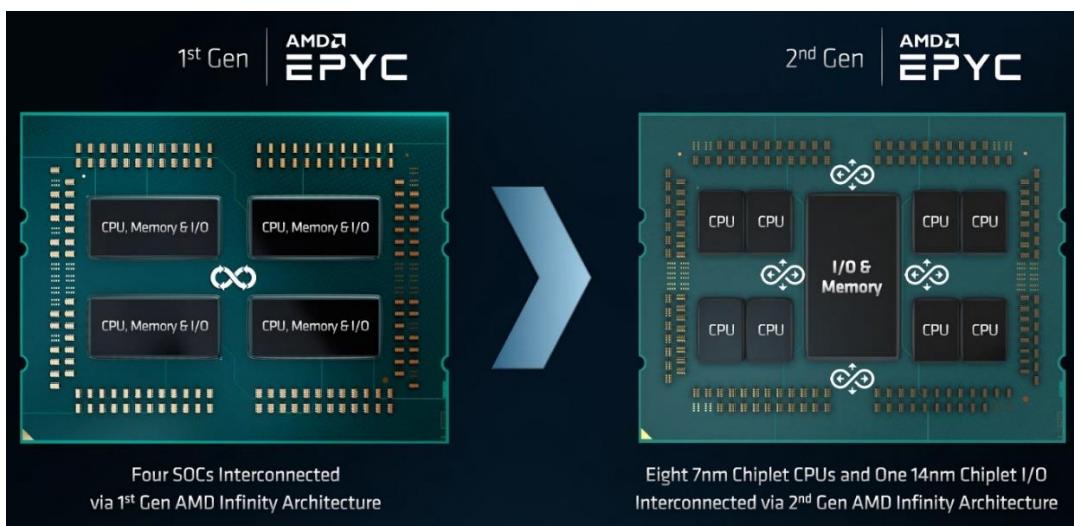

Технология СвК – это комбинация в одном модуле сразу нескольких активных и пассивных электронных компонентов, выполняющих разные функции. На сегодняшний день наиболее интересным и освоенным направлением СвК получило направление, называемое чиплет (chiplet). Чиплет – это кристалл, специально разработанный для функционирования с другими подобными кристаллами на одной подложке. На рисунке 5 приведен пример процессора фирмы

AMD Ryzen Threadripper, выполненный по технологии чиплетов [4].

Рис. 5. Процессор фирмы AMD Ryzen Threadripper, выполненный по технологии чиплетов

На рисунке 6 AMD представляет следующий шаг фирмы AMD по развитию своего чиплетного процессора [4]. Происходит дальнейшая дезинтеграция больших кристаллов. В отдельные чиплеты выделяются центральные процессы, изготавливаемые по технологии 7 нм. В

результате их количество возросло до 8 штук. Память и контроллеры ввода/вывода выделены в отдельный чиплет, выполненный по более дешевой технологии 14 нм.

Рис. 6. Развитие чиплетного процессора фирмы AMD Ryzen Threadripper

Технология чиплетов показывает удивительную гибкость:

- можно умножать количество процессорных ядер при помощи чиплетов до необходимого количества для решения поставленной задачи;

- можно одновременно использовать разные чиплеты на базе передовых и предыдущих технологий, что даёт выигрыш в цене и надёжности микросхемы;

- можно одновременно использовать чиплеты, выполненные по разным технологиям

- Si, GaAs, SiGe и др;

- можно одновременно использовать как цифровые чиплеты, так и аналоговые, разнообразные сенсоры, радиочастотные тракты, микроэлектромеханические системы (МЭМС) и т. д., изготовленные по наиболее подходящим для них технологиям.

Дополнительные преимущества чиплетов:

- использование небольших чиплетов заметно снижает уровень брака по сравнению с большими кристаллами СиК, что снижает

стоимость конечного продукта;

- уменьшение размеров кристаллов на пластине позволяет повысить заполняемость на краях пластины по сравнению с крупными кристаллами, что положительно сказывается на цене кристаллов.

## 5. Заключение

В статье приведены особенности полимерных и LTCC подложек для перевёрнутых кристаллов. Описан опыт в области разработки и эксплуатации микросхем в ФГУ ФНЦ НИИСИ РАН. Обозначены тенденции

развития технологии производства кристаллов. Обоснован переход производителей сложных микросхем от «системы на кристалле» к многокристальной «системы в корпусе». Представлены преимущества применения чиплетов в сложных микросхемах.

Публикация выполнена в рамках государственного задания ФГУ ФНЦ НИИСИ РАН по теме № FNEF-2024-0003 "Методы разработки аппаратно-программных платформ на основе защищенных и устойчивых к сбоям систем на кристалле и сопроцессоров искусственного интеллекта и обработки сигналов".

# Challenges and Directions of Development of Microchips with a Flip-Chip Technology

**A.M. Baranov, A.A. Podkovyrov, A.V. Andreev**

**Abstract.** The paper discusses the challenges and directions of development of microchips with a flip-chip technology. The features and properties of polymer and LTCC substrates are considered. The main characteristics of microchips developed at the SRISA RAS are presented. The "System-in-Package" technology and its advantages are described.

**Keywords:** Flip-Chip technology, LTCC packages, organic packages, System-in-Package

## Литература

1. Баранов А.М., Подковыров А.А., Андреев А.В. Опыт НИИСИ РАН по разработке подложек для микросхем с перевернутым кристаллом. Труды НИИСИ РАН. 2023. Т. 13. № 3. С. 30-35.

2. Гусева М.А. Циановые эфиры – перспективные термореактивные связующие (обзор) // Авиационные материалы и технологии. 2015. №2 (35). С. 45-50.

3. Как умирал Закон Мура или эволюция транзисторов: от 2D к 3D. URL: <https://club.dns-shop.ru/blog/t-100-protsessoryi/73291-kak-umiral-zakon-mura-ili-evolutsiya-tranzistorov-ot-2d-k-3d/>. (дата обращения 12.02.2024)

4. Что такое чиплет? Преимущества и недостатки чиплетного дизайна. URL: <https://club.dns-shop.ru/blog/t-100-protsessoryi/71441-cto-takoe-chiplet-preimuschestva-i-nedostatki-chipletnogo-dizaina/> (дата обращения 15.02.2024)