# Использование при разработке СнК метода программной инжекции сбоев для оценки перехода на технологию с меньшими проектными нормами

П.О. Черняков<sup>1</sup>, А.П. Скоробогатов<sup>2</sup>

<sup>1</sup>ФГУ ФНЦ НИИСИ РАН, Москва, Россия, <a href="mailto:chernyakov@cs.niisi.ras.ru">chernyakov@cs.niisi.ras.ru</a>; <sup>2</sup>ФГУ ФНЦ НИИСИ РАН, Москва, Россия, <a href="mailto:skorobog\_a@cs.niisi.ras.ru">skorobog\_a@cs.niisi.ras.ru</a>;

Аннотация. В данной работе представлен подход к оценке достаточности применяемых мер парирования сбоев в цифровых блоках систем на кристалле (СнК) при переходе на технологию с меньшими проектными нормами и целесообразности данного перехода при условии сохранения прежнего уровня сбоеустойчивости. Подход основан на методе программной инжекции сбоев и продемонстрирован на примере переноса контроллера внешней статической памяти с технологии с 250 нм проектными нормами на технологию с 65 нм проектными нормами.

**Ключевые слова:** резервирование, TMP, SEU, SET, инжекция сбоев

# 1. Введение

Повышение требований к производительности микроэлектронной ЭКБ – один из основных стимулов развития технологий интегральных схем. Перенос проекта микросхемы на технологию с меньшими проектными нормами позволяет достичь лучших характеристик по рабочей частоте и энергопотреблению, а также усложнить функциональность за счет использования большего числа транзисторов на единицу площади. Одной из значимых характеристик схемы, ухудшающихся при переходе на технологию с меньшими проектными нормами, является сбоеустойчивость. Для разработок, предназначенных для использования в космической электронике, при переходе на меньшие технологические нормы необходимо использовать дополнительные меры по парированию сбоев [1]. Тройное модульное резервирование (ТМР) является эффективным и одним из наиболее распространенных методов парирования сбоев, однако негативно сказывается на характеристиках схемы, таких как быстродействие и энергопотребление, что может нивелировать преимущества от перехода на меньшие проектные нормы. Кроме этого, разработка и производство микросхемы, а также её испытание на стойкость к одиночным эффектам, требуют больших временных и материальных затрат. Следовательно, необходимо иметь возможность оценки достаточности мер по парированию сбоев и ожидаемых преимуществ от перехода на меньшие проектные нормы ещё на этапе разработки микросхемы.

В данной работе с использованием инструмента для инжекции сбоев на этапе логического моделирования [2], [3] сравниваются реализация контроллера внешней статической памяти, разработанная по технологии 250 нм КНИ, с несколькими реализациями этого контроллера, разработанными по 65 нм объемной технологии, отличающимися различными мерами парирования сбоев. Оценивается выигрыш в быстродействии при переходе на технологию с проектными нормами 65 нм при условии сохранения сбоеустойчивости как минимум на уровне реализации на 250 нм. Данная статья — полная версия работы, представленной на конференции «Стойкость-2021» [4].

# 2. Тестируемое устройство

В качестве объекта для исследования был выбран СФ-блок контроллера внешней статической памяти, являющийся типовым блоком систем на кристалле и обладающий относительно невысокой сложностью и небольшим размером, что делает его удобным для моделирования. В составе данного блока присутствуют только триггеры и ячейки комбинационной логики и отсутствуют вложенные СФ-блоки и памяти.

Были подготовлены несколько различных топологических реализаций данного блока. Одна реализация по 250 нм КНИ КМОП технологии без дополнительных мер парирования сбоев, а также четыре реализации по 65 нм объемной КМОП технологии:

- 1) без мер парирования сбоев;

- с применением локального ТМР (ЛТМР): троируются только триггеры,

- комбинационная логика, включая ячейки дерева синхросигналов, остается в единственном экземпляре;

- с применением распределенного ТМР (РТМР): троируются триггеры и комбинационная логика, исключая ячейки дерева синхросигналов, остающиеся в единственном экземпляре;

- с применением глобального ТМР (ГТМР): троируются все логические компоненты блока [5].

При разработке реализаций ставилась цель достичь схожей плотности размещения элементов на топологии. Также задавались схожие временные ограничения (constraints) на входные и выходные сигналы в процентах от тактового сигнала. Характеристики получившихся реализаций приведены в таблице 1.

Таблица 1. Основные характеристики тестируемых реализаций

| Реали-<br>зация     | Площадь,<br>10 <sup>5</sup> мкм <sup>2</sup> | Плотность<br>размеще-<br>ния, % | Ча-<br>стота,<br>МГц |

|---------------------|----------------------------------------------|---------------------------------|----------------------|

| КНИ<br>250 нм       | 7,93                                         | 77,4                            | 44                   |

| Без<br>ТМР<br>65 нм | 1,37                                         | 74,8                            | 166                  |

| ЛТМР<br>65 нм       | 2,16                                         | 76,7                            | 149                  |

| РТМР<br>65 нм       | 4,22                                         | 78,1                            | 128                  |

| ГТМР<br>65 нм       | 4,34                                         | 77,8                            | 123                  |

### 3. Тестовая система

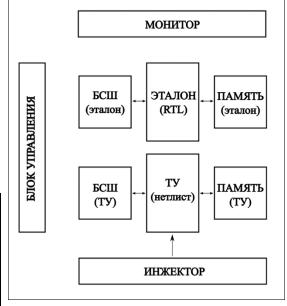

В составе тестовой системы, представленной на рисунке 1, можно выделить несколько основных блоков:

- 1) тестируемое устройство с необходимым тестовым окружением;

- эталонное устройство с аналогичным тестовому устройству окружением;

- 3) блок инжекции сбоев;

- 4) монитор;

- 5) блок управления.

Тестируемое устройство (ТУ) – одна из реализаций контроллера памяти в виде нетлиста. К тестируемому устройству подключается блок

системной шины (БСШ) и модуль памяти, с которыми ТУ взаимодействует в рамках теста.

Эталонное устройство – RTL-модель контроллера памяти. Эталонное устройство соединено с собственными экземплярами памяти и БСШ

Блок инжекции сбоев или инжектор – специальный программный инструмент, позволяю-

Рис. 1. Структура тестовой системы

щий при моделировании вносить сбои в элементы нетлиста, в том числе с учетом их расположения. Для внесения сбоев строится квадратная область заданного размера, после чего отбираются ячейки, полностью или частично попадающие в данную область. Половину стороны данной области назовем радиусом внесения сбоев. Таким образом можно моделировать множественные сбои от попадания одной частицы. Сбой в триггере (SEU) моделируется как изменение его логического состояния на противоположное. Сбой в комбинационном элементе (SET) моделируется как временное изменение значения его выхода на противоположное.

Монитор отвечает за сравнение результатов теста у тестируемого и эталонного устройств.

Блок управления отвечает за подготовку и запуск тестов на тестируемом и эталонном устройствах.

В качестве тестов выступают простейшие запросы от блока системной шины к контроллеру памяти на чтение или запись данных.

В каждом цикле работы тестовой системы сначала тест запускается на эталонной модели контроллера, после завершения теста фиксируется состояние блока системной шины и модуля памяти эталонного контроллера, а также продолжительность выполнения теста. Затем этот тест

запускается на тестируемом устройстве. В случайный момент времени с помощью инжектора вносятся сбои в тестируемое устройство, координата для внесения сбоев выбирается случайным образом. По завершению теста состояние блока системной шины и модуля памяти тестируемого устройства сравниваются с состоянием аналогичных блоков эталонного устройства. В случае отличий, а также при зависании тестируемого устройства фиксируется ошибка. После выполнения цикла тестовые окружения тестируемого и эталонного устройств приводятся в одинаковое состояние, а сами устройства сбрасываются. После этого может запускаться следующий цикл. Для каждой реализации контроллера памяти запускались 10<sup>5</sup> циклов тестирования.

# 4. Выбор параметров для инжекции

Одной из основных сложностей при использовании инжектора сбоев, особенно в случае сравнения реализаций на различных технологиях, является выбор корректных параметров для моделирования: радиуса области внесения сбоев и длительности импульса переходного процесса. Это связано с недостаточностью экспериментальных данных по определению этих характеристик для микросхем, изготовленных по различным технологиям.

Длительность импульса переходного процесса в общем случае зависит от емкостей и сопротивлений элементов в технологии, а также от напряжения питания. Для различных технологий характерная длительность импульса будет отличаться.

Радиус внесения сбоев для 250 нм КНИ технологии обусловлен только радиусом трека частицы. В 65 нм объемной КМОП технологии присутствует также диффузия заряда между транзисторами (эффект «растекания» заряда по подложке), поэтому радиус внесения сбоев будет больше.

В рамках типичной ячейки логического элемента в каждый момент времени не вся площадь является чувствительной областью. Для реализации по объемной 65 нм технологии этим можно пренебречь, поскольку, учитывая типичный размер ячейки, область сбоев одновременно перекрывает большое число ячеек; для реализации по 250 нм КНИ КМОП технологии необходимо вводить поправочный коэффициент.

Для моделирования реализаций контроллера по технологии 65 нм был выбран радиус внесения сбоев 1 мкм и длительность импульса 100 пс [6], сбои вносятся во все отобранные по критерию пересечения с областью сбоев ячейки. В случае технологии КНИ 250 нм рассматривались

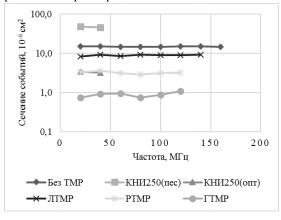

2 случая: условно пессимистичный и условно оптимистичный. В условно пессимистичном случае длительность импульса была аналогична технологии 65 нм (100 пс), радиус выбран 100 нм. В условно оптимистичном случае сбои вносились только в триггеры, радиус был выбран равным 1 нм, что равносильно внесению сбоя только при непосредственном попадании в элемент. Дополнительно для оптимистичного случая вводился поправочный коэффициент, который учитывает, что не вся площадь триггера является чувствительной. Коэффициент равен сумме площадей стоков и затворов транзисторов, деленных на 4 и на площадь триггера. Для наиболее распространенного в рассматриваемой топологии триггера коэффициент равен 0,073. Результаты моделирования представлены в таблице 2 и на рисунке 2.

# 5. Результаты моделирования и анализ

Таблица 2. Значение наибольшего сечения событий

| Реализация              | Наибольшее се-<br>чение событий,<br>10 <sup>-6</sup> см <sup>2</sup> | Частота<br>худшего се-<br>чения со-<br>бытий,<br>МГц |

|-------------------------|----------------------------------------------------------------------|------------------------------------------------------|

| КНИ 250 нм<br>(пессим.) | 47,82                                                                | 20                                                   |

| КНИ 250 нм<br>(оптим.)  | 3,38                                                                 | 20                                                   |

| Без ТМР<br>65 нм        | 15,11                                                                | 40                                                   |

| ЛТМР 65 нм              | 9,36                                                                 | 80                                                   |

| РТМР 65 нм              | 3,59                                                                 | 40                                                   |

| ГТМР 65 нм              | 1,09                                                                 | 120                                                  |

В таблице 2 для каждой реализации приведены: наибольшее полученное сечение событий и частота, при котором это сечение получено. На рисунке 2 показаны зависимости сечений событий от частоты для каждой реализации.

По результатам видно, что, по пессимистичной оценке, реализация по КНИ 250 нм оказывается по сбоеустойчивости хуже остальных вариантов.

Если рассматривать оптимистичный вариант оценки реализации по КНИ 250 нм, то он оказывается заметно лучше, чем варианты по 65 нм

без ТМР и с локальным ТМР, а также немного лучше, чем с распределенным ТМР. Но даже оптимистичный вариант КНИ250 заметно уступает варианту по 65 нм с глобальным ТМР. При этом максимальная частота ГТМР почти в три раза выше. Из этого можно сделать вывод, что с точки зрения сочетания производительности и сбоеустойчивости, переход с 250 нм КНИ КМОП технологии на 65 нм объемную КМОП технологию для данного контроллера оправдан, так как при условии использования глобального ТМР можно добиться повышения максимальной частоты примерно в три раза при большей сбоеустойчивости.

По рисунку 2 видно, что отсутствует явная зависимость сечений событий от частоты. Это можно объяснить высокой функциональной сложностью блока, а также тем, что в вариантах по 65 нм большое значение имеют множественные сбои.

Важно отметить, что полученные значения сечений событий имеют сильную зависимость не только от выбора параметров инжектора (радиуса внесения сбоев, длительности импульса переходного процесса и поправочного коэффициента), но также от набора тестов и параметров работы контроллера.

Рис. 2. График зависимости сечения событий от частоты

Рассматриваемый в данной работе СФ-блок контроллера памяти имеет большое число различных настроечных регистров, вариантов подключения памяти и режимов работы с памятью. При этом в тестовой системе использовались лишь самые простые запросы на чтение и запись для одной из возможных конфигураций контроллера. Такие тесты не покрывают всю функциональность и все сочетания различных параметров контроллера. Используя при тестировании

другие наборы тестов, можно получить значения сечений, отличающиеся от полученных в данной работе. Поэтому для более точной и надежной оценки предлагается использовать более комплексные наборы тестов, покрывающие не только типичные варианты работы. В том числе можно определить те тесты и режимы, где наблюдаются наихудшие значения сечений событий, и учитывать их в оценке.

## 6. Заключение

На примере переноса контроллера внешней статической памяти с 250 нм КНИ на 65 нм объемную КМОП технологию представлен подход к оценке целесообразности такого перехода с точки зрения повышения производительности при условии сохранения прежнего уровня сбоеустойчивости.

Для этого были подготовлены и промоделированы с внесением сбоев несколько различных реализаций данного контроллера: реализация по 250 нм КНИ технологии без мер парирования сбоев, уровень сбоеустойчивости которой был принят за референсную точку, и четыре реализации по 65 нм объемной технологии с различными реализациями защиты от сбоев.

По результатам моделирования и анализа был сделан вывод, что такой переход для данного контроллера целесообразен, так как при условии применения глобального ТМР (ГТМР) на 65 нм объемной технологии удалось достичь втрое большей частоты при большем уровне сбоеустойчивости.

Были отмечены основные сложности данного подхода, связанные с обоснованным выбором для различных технологий параметров моделирования: радиуса внесения сбоев, длительности импульса переходного процесса и поправочного коэффициента, учитывающего реальный размер чувствительной области в элементах.

Также было отмечено, что значение сечения событий для одной и той же реализации СФ-блока может отличаться в зависимости от режимов работы и используемых тестов. При выборе оптимальной реализации рекомендуется ориентироваться на более комплексные наборы тестов.

Публикация выполнена в рамках государственного задания ФГУ ФНЦ НИИСИ РАН по теме FNEF-2022-0008.

# Using Fault Injection Technique in SoC Design Flow to Evaluate Shifting to a Smaller Technology Node

P. Chernyakov, A. Skorobogatov

**Abstract.** This paper presents an approach to assessing the sufficiency of the measures used to mitigation faults in digital blocks of system-on-chip (SoC) during the shifting to technology with smaller technology node and the feasibility of this shifting, provided that the previous level of fault tolerance is maintained. The approach is based on the fault injection technique and is demonstrated by the example of shifting an external static memory controller from 250 nm to 65 nm technology.

Keywords: redundancy, TMR, SEU, SET, fault injection

# Литература

- 1. P. E. Dodd, M. R. Shaneyfelt, J. R. Schwank, J. A. Felix. Current and future challenges in radiation effects on cmos electronics. "IEEE Transactions on Nuclear Science", V. 57 (2010), No. 4, 1747–1763. ISSN:0018-9499. DOI: 10.1109/TNS.2010.2042613.

- 2. И.А. Данилов, А.И. Шнайдер (Хазанова), А.О. Балбеков, М.С. Горбунов, А.А. Антонов. Маршрут разработки сбоеустойчивых СБИС с помощью программной инжекции сбоев с учетом топологии. «Вопросы атомной науки и техники. Сер.: Физика радиационного воздействия на радио-электронную аппаратуру», 2019, Вып. 4, 5–10.

- 3. P. Chernyakov et al. Comparative Analysis of Layout-Aware Fault Injection on TMR-based DMA Controllers, "2019 IEEE 31st International Conference on Microelectronics (MIEL)", Nis, Serbia, 2019, 289–292. DOI: 10.1109/MIEL.2019.8889643.

- 4. П.О. Черняков, А.П. Скоробогатов. Баланс сбоеустойчивости и быстродействия при переходе от 250 нм КНИ к 65 нм объемной КМОП технологии на примере контроллера памяти. «Радиационная стойкость электронных систем «Стойкость-2021»: 24-я Всероссийская научно-техническая конференция. Лыткарино, 8–9 июня 2021 г. (тезисы)», Лыткарино, Изд-во Научно-исследовательский институт приборов, 2021, 26–27.

- 5. M. D. Berg, H. S. Kim, A. M. Phan, C. M. Seidleck, K. A. LaBel, J. A. Pellish, M. J. Campola. The effects of race conditions when implementing single-source redundant clock trees in triple modular redundant synchronous architectures. "Proceedings, 16th European Conference on Radiation and its Effects on Components and Systems (RADECS 2016)", Germany, Bremen, 2016.

- 6. A. Evans, M. Glorieux, D. Alexandrescu, C.B. Polo, V. Ferlet-Cavrois. Single event multiple transient (SEMT) measurements in 65 nm bulk technology. "Proceedings, 16th European Conference on Radiation and its Effects on Components and Systems (RADECS 2016)", Germany, Bremen, 2016.