# 12-разрядный аналого-цифровой преобразователь конвейерного типа

#### Ю.Б. Рогаткин

НИЦ «Курчатовский институт» — НИИСИ, Москва, Российская Федерация; ryb@cs.niisi.ras.ru;

**Аннотация**. Представлен КМОП 12-разрядный аналого-цифровой преобразователь конвейерного типа с проектными нормами 28 нм. Сравнительно низкое энергопотребление при достаточно высокой частоте дискретизации до 125 МГц достигается за счет использования в конвейерной архитектуре полностью дифференциальных двухкаскадных операционных усилителей, работающих в конвейерной архитектуре АЦП 1,5 бита на каскад с напряжением питания 1,8В.

Ключевые слова: аналого-цифровой преобразователь, частота дискретизации, разрядность.

### 1. Введение

Поскольку сигналы реального времени всегда являются аналоговыми по своей природе, существует необходимость преобразования этих аналоговых величин в цифровой сигнал, соответствующий любому применению. Аналогоцифровой преобразователь (АЦП) — это устройство, которое преобразует аналоговый сигнал, такой как напряжение или ток, в цифровой сигнал (т.е. представляет его в двоичном виде -0 и 1). Таким образом, преобразование аналогового сигнала в цифровой обычно выполняется с помощью преобразователей данных. Аналогоцифровой и цифроаналоговый преобразователь (ЦАП) — это два очевидных типа преобразователей данных, каждый из которых применяется в соответствии с требуемым применением. При проектировании сенсорной сети, АЦП играют очень важную роль. Сигналы, получаемые от датчика, дискретизируются, квантуются и кодируются, а эквивалентный цифровой сигнал получается с помощью стандартного аналого-цифрового преобразователя. Как правило, чтобы избежать наложения, дискретизация входного сигнала должна выполняться со скоростью, более чем в два раза превышающей полосу пропускания входного аналогового сигнала. Однако, бывают применения, когда АЦП работает в режиме субдискретизации, когда спектр входного сигнала лежит в полосе, соответствующей более высокой зоне Найквиста, чем первая. В этом случае важную роль играет полоса пропускания АЦП (Analog Bandwidth) [1]. По сравнению с другими АЦП, в конвейерных АЦП используется меньшее количество компараторов, что приводит к меньшей задержке. В портативных устройствах передачи данных и системах беспроводной связи конвейерный АЦП является

важным компонентом, поскольку он может выдавать выходные данные с высокой скоростью и разрешением. Чтобы обеспечить наилучшее соотношение между скоростью и разрешением для достижения оптимальных условий, используется конвейерный АЦП. Это приводит к достижению идеального размера микросхемы и относительно небольшому рассеиванию мощности [2].

# 2. Архитектура и конструкция АЦП

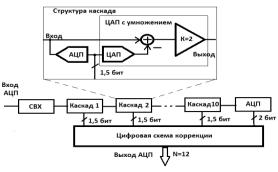

Одна из простейших реализаций конвейерных АЦП, включающих цифровую коррекцию (резервирование), основана на архитектуре с производительностью 1,5 бита на каскад, показанной на рис. 1. Эта архитектура традиционно широко используется для увеличения скорости преобразования [3].

Рис.1.Используемая архитектура в конвейерном АЦП

### 2.1. Операционный усилитель

Операционный усилитель является одним из наиболее важных компонентов конвейерных АЦП. Коэффициент усиления по постоянному

току и полоса пропускания операционного усилителя определяют достижимую точность и скорость преобразования. Для 12-разрядного конвейерного АЦП коэффициент усиления операционного усилителя с разомкнутым контуром должен быть не менее 70 дБ. Нередко, в практических примерах проектирования можно увидеть коэффициент усиления в 80 дБ. Разработка такого операционного усилителя с высоким коэффициентом усиления при низком напряжении питания является довольно сложной задачей, поскольку традиционное расположение каскадных транзисторов неосуществимо. Использование многокаскадных операционных усилителей с компенсацией приведет к значительному увеличению мощности потребление и снижению скорости. В описываемом АЦП использован полностью дифференциальный двухкаскадный операционный усилитель КМОП, который работает от источника питания 1,8 В. Операционный усилитель обеспечивает коэффициент усиления не менее 80 дБ, частоту единичного усиления не менее 1 ГГц при нагрузке 0,7 пФ и скорость нарастания выходного напряжения до 1000 В/мкс. Потребляемая мощность операционного усилителя составляет не более 8 мВт [4]. Параметры операционного усилителя сведены в таблицу 1.

Таблица 1

| Параметр                                        | Мин.<br>зна-<br>чение | Макс.<br>значе-<br>ние | Единица<br>измере-<br>ния |

|-------------------------------------------------|-----------------------|------------------------|---------------------------|

| Напряжение сме-<br>щения                        | -232                  | -35                    | мкВ                       |

| Запас по фазе                                   | 37                    | 79                     | градус                    |

| Частота единич-<br>ного усиления                | 1,14                  | 3,88                   | ГГц                       |

| Полоса пропус-<br>кания по уровню<br>-3 дБ      | 63                    | 160                    | кГц                       |

| Скорость нарастания выходного напряжения (2)    | 443                   | 1018                   | В/мкс                     |

| Время установ-<br>ления <sup>(2)</sup>          | 1,72                  | 5,01                   | нс                        |

| Дифференциаль-<br>ный коэффици-<br>ент усиления | 79,2                  | 94,4                   | дБ                        |

| Коэффициент ослабления синфазного сигнала       | 72,8                  | 85,9                   | дБ                        |

| Коэффициент подавления нестабильности питания   | 68,8                  | 100,8                  | дБ                        |

| Ток потребления                                 | 2,68                  | 4,19                   | мА                        |

### 2.2. ЦАП с умножением

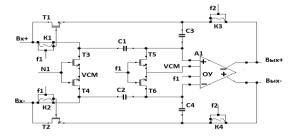

На рисунке 2 показан умножающий цифроаналоговый преобразователь (MDAC), который является полностью дифференциальной схемой.

Рис2. Полностью дифференциальный умножающий цифроаналоговый преобразователь

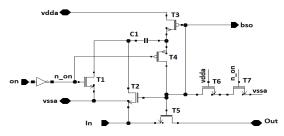

В качестве переключающих элементов использовался ключ типа «bootstrap switch», принципиальная схема которого приведена на рисунке 3.

Рис.3. Элемент переключения для MDAC

В момент отпирания коммутирующего транзистора Т5 напряжение на его затворе составляет

$$Vg5 = Vs5 + \frac{c_1}{c_{1}+c_p}Vdda \tag{1}$$

где Cp - общая паразитная емкость, подключенная к верхней пластине конденсатора C1.

В качестве последнего каскада в конвейере АЦП используется 2-х разрядный параллельный аналого-цифровой преобразователь.

### 2.3. Топология АЦП

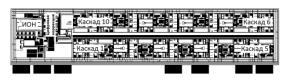

На рисунке 4 приведена топология СФ-блока КМОП 12-разрядного аналого-цифрового преобразователя конвейерного типа с проектными нормами 28 нм.

Рис.4. Топология АЦП

Размеры СФ-блока без площадок составляют 630x150 мкм.

## 3. Результаты моделирования

# 3.1. Встроенный источник опорного напряжения

Внутренний источник опорного напряжения (ИОН), вырабатывает высокое опорное напряжения VRP = +1,3 В и низкое опорное напряжения VRM = +0,5 В, которые, собственно, и определяют шкалу АЦП. В блоке ИОН имеется возможность тонкой подстройки величины опорного напряжения и его температурной зависимости. Максимальный температурный дрейф в диапазоне от минус  $40 \, \text{C}^{\circ}$  до плюс  $90 \, \text{C}^{\circ}$  не превышает  $15 \, \text{ppm/C}^{\circ}$ .

### 3.2. Параметры АЦП

Проводилось моделирование АЦП с учетом паразитных элементов конструкции (топологии): резисторов и конденсаторов. Моделирование проводилось в температурном диапазоне от -40  $^{\circ}$  С до +90  $^{\circ}$ , с разбросом питающего напряжения от +1,7 B до +1,9 B и для различных технологических процессов, всего 17 углов. Кроме того, использовался вероятностный метод расчетов Монте Карло.

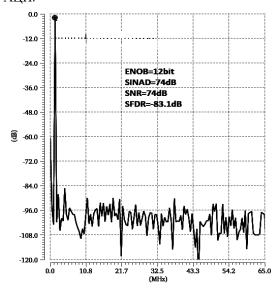

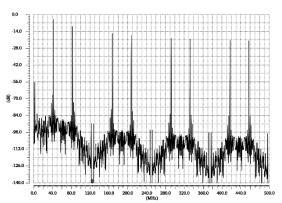

На рис.5 приведен пример спектра аналогового эквивалента выходного цифрового сигнала АЦП.

Рис. 5. Спектр аналогового эквивалента выходного цифрового сигнала АЦП.

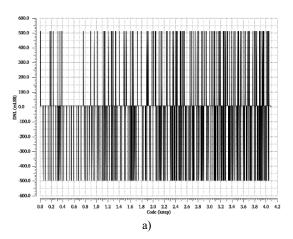

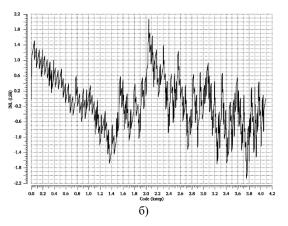

Исследовались статические характеристики АЦП: DNL и INL.

Рис. 6. Статические характеристики АЦП: а -зависимость DNL от выходного кода; б - зависимость INL от выходного кода.

В таблице 2 приведены параметры АЦП при нормальных условиях.

Таблица.2

| Параметр   | Процесс ТТ, Fsampl=125МГц |              |              |

|------------|---------------------------|--------------|--------------|

|            | +1,8B; +27C°              |              |              |

|            | Выборка<br>1              | Выборка<br>2 | Выборка<br>3 |

| ENOB       | 12,00                     | 11,97        | 11,98        |

| SINAD, dB  | 74,00                     | 73.85        | 73.86        |

| SNR, dB    | 74,00                     | 73.85        | 73.86        |

| SFDR, dB   | -83,13                    | -82.24       | -82.25       |

| Ipower, mA | 34,24                     | 34,24        | 34,23        |

В таблице 3 приведены максимальные отклонения параметров АЦП при всевозможных условиях моделирования в упомянутых выше 17 углах.

| <b>TD</b> | _    | _   |

|-----------|------|-----|

| I a       | опин | ล ร |

| Параметр                | Минимальное<br>значение<br>параметра | Максимальное<br>значение<br>параметра |

|-------------------------|--------------------------------------|---------------------------------------|

| ENOB                    | 10                                   | 12                                    |

| SINAD, dB               | 60,4                                 | 74,5                                  |

| SNR, dB                 | 60,4                                 | 74,5                                  |

| SFDR, dB                | -85,5                                | -64,0                                 |

| I <sub>power</sub> , mA | 24,7                                 | 57,4                                  |

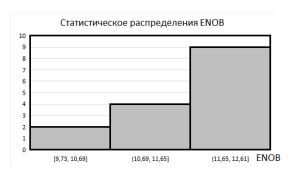

На рисунке 7 приведено статистическое распределение значение ENOB для 15 выборок в различных углах моделирования.

Рис.7. Статистическое распределение значение ENOВ для 15 выборок.

## 3.3. Работа АЦП в режиме субдискретизации

Как упоминалось выше, полоса пропускания АЦП (**FPBW** — Full Power (Analog) Bandwidth) является очень важным параметром при построении систем, которые работают в режиме субдискретизации. Можно оценить минимально возможное значение полосы пропускания для данного АЦП [5]. За период выборки емкость СВХ должна зарядиться с точностью до одного LSB. Если период выборки равен 1/(2Fs), где Fs частота выборок, то ошибка выборки сигнала полной шкалы  $V_{FS}$  равна:

$$V_{FS} \times \exp\left(-\frac{t}{\tau}\right) = 1 \times LSB$$

лной шкалы

$$V_{FS}$$

равна:

$$V_{FS} \times \exp\left(-\frac{t}{\tau}\right) = 1 \times LSB$$

Решив относительно t, получаем:

$$t = -\tau \times \ln\left(\frac{1 \times LSB}{V_{FS}}\right)$$

Положив, что  $\tau = 1/2\pi FPBW$ , определим минимальную полосу АЦП для  $t=1/(2F_s)$

FPBW =

$$-\left(\frac{F_S}{\pi}\right) \times \ln\left(\frac{1 \times LSB}{V_{FS}}\right)$$

(2)

Для представленного 12 разрядного АЦП с

частотой дискретизации 125 Мвыб/с и шкалой 800мВ ограничение снизу для полосы пропускания, рассчитанное по формуле (2) составит FPBW=331 МГц. Следует учитывать, что динамические параметры АЦП как правило ухудшаются с ростом частоты входного сигнала, поэтому оцифровать сигнал из 6-й зоны так же качественно, как из 1-й не получится. На рисунке 8 приведен спектр выходного сигнала при частоте входного сигнала  $F_{in}$ =290 МГц. Видно, что в высших зонах Найквиста величина оцифрованного входного сигнала меньше, чем в низших зонах Найквиста.

Рис. 8. Работа АЦП с частотой входного сигнала вне первой зоны Найквиста.

### 4. Заключение

В этой статье описывается конструкция конвейерного 12-разрядного АЦП с частотой дискретизации до 125 Мвыб/с, реализованного по КМОП технологии с проектными нормами 28 нм. Показано, что конвейер с переключаемым конденсаторами на 1,5-битных каскадах способен обеспечить линейность 12-разрядного сигнала без искажений или калибровки. Низкое энергопотребление до 100 МВт достигается за счет выбора конфигурации ОУ и оптимизированного по мощности разрешения для первого каскада.

Публикация выполнена в рамках государственного задания НИЦ «Курчатовский институт» — НИИСИ по теме № FNEF-2024-0003 «Методы разработки аппаратно-программных платформ на основе защищенных и устойчивых к сбоям систем на кристалле и сопроцессоров искусственного интеллекта и обработки сигналов».

# 12-bit analog-to-digital converter of conveyor type

### Y.B. Rogatkin

**Abstract.** A CMOS 12-bit analog-to-digital converter of conveyor type with design standards of 28 nm is presented. Comparatively low power consumption with a sufficiently high sampling frequency of up to 125 MHz is achieved through the use of fully differential two-stage operational amplifiers in the pipeline architecture, operating in a 1.5-bit ADC pipeline architecture per stage with a supply voltage of 1.8V.

**Keywords:** analog-to-digital converter, sampling rate, bit depth.

# Литература

- 1. Улучшение оцифровки с помощью передискретизации и усреднения, https://microsin.net/programming/dsp/an118-improving-adc-resolution-by-oversampling-and-veraging.html (дата обращения 15.08.2025).

- 2. Sivaram Prasad Kopparthy,Ishit Makwana, Anu Gupta." Asynchronous 8-bit pipelined ADC for self-triggered sensor based applications", Asia Pacific Conferenceon Postgraduate Research in Microelectronics and Electronics, 2012.

- 3. S. Lewis et al., "A 10-b 20 MSamples/s analog to digital converter," IEEE J. Solid-State Circuits, vol. 27, pp. 351–358, Mar. 1992.

- 4. Ю.Б.Рогаткин. Двухкаскадный операционный усилитель для аналого-цифрового преобразователя конвейерного типа. «Нано- и микросистемная техника», 2025, №4, с.201-208.

- 5. https://habr.com/ru/companies/milandr/articles/528164 (дата обращения 15.08.2025).